機(jī)器視覺在工業(yè)自動(dòng)化系統(tǒng)中的應(yīng)用已經(jīng)有一些的歷史,它取代了傳統(tǒng)的人工檢查,提高了生產(chǎn)質(zhì)量和產(chǎn)量。 我們已經(jīng)看到了相機(jī)在計(jì)算機(jī)、移動(dòng)設(shè)備和汽車等日常生活設(shè)備中的迅速普及,但是機(jī)器視覺的最大進(jìn)步莫過于處理能力。

隨著處理器的性能以每?jī)赡攴环乃俣炔粩嗵嵘约岸嗪薈PU和FPGA等并行處理技術(shù)日益受到關(guān)注,視覺系統(tǒng)設(shè)計(jì)人員現(xiàn)在可以應(yīng)用復(fù)雜的算法來可視化數(shù)據(jù),并創(chuàng)建出更加智能的系統(tǒng)。

性能的提高意味著設(shè)計(jì)人員可以獲得更高的數(shù)據(jù)吞吐量,從而實(shí)現(xiàn)更快速的圖像采集,使用更高分辨率的傳感器,并充分利用市場(chǎng)上具有最高動(dòng)態(tài)范圍的一些新款相機(jī)。性能的提高不僅可讓設(shè)計(jì)人員更快速地采集圖像,而且還能更快速地處理圖像。預(yù)處理算法(如閾值和濾波)或處理算法(如模式匹配)也可以更快速地執(zhí)行。最終設(shè)計(jì)人員能夠比以往更快地基于可視化數(shù)據(jù)制定決策。

隨著視覺系統(tǒng)越來越多地集成最新一代多核CPU和強(qiáng)大FPGA,視覺系統(tǒng)設(shè)計(jì)人員需要了解使用這些處理元件的好處和得失。他們不僅需要在正確的硬件上運(yùn)行正確的算法,還需要了解哪些架構(gòu)最適合作為其設(shè)計(jì)的基礎(chǔ)。

1、內(nèi)聯(lián)處理和協(xié)處理

在研究哪種類型的算法最適合哪個(gè)處理元件之前,您應(yīng)該了解每個(gè)應(yīng)用最適合的架構(gòu)類型。在開發(fā)基于CPU和FPGA的異構(gòu)架構(gòu)的視覺系統(tǒng)時(shí),需要考慮兩個(gè)主要的使用情況: 嵌入式處理和協(xié)處理。

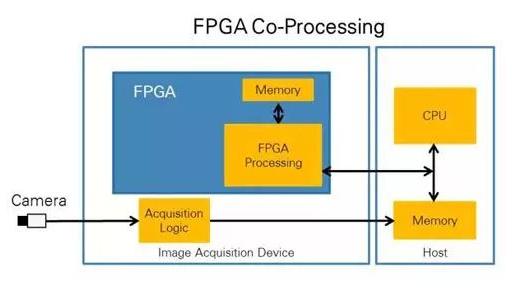

如果是FPGA協(xié)處理,F(xiàn)PGA和CPU將共同工作,共享處理負(fù)載。這種架構(gòu)最常用于GigE Vision和USB3 Vision相機(jī),因?yàn)樗鼈兊牟杉壿嬜詈檬窃贑PU上實(shí)現(xiàn):

您可以使用CPU采集圖像,然后通過直接存儲(chǔ)器訪問(DMA)將其發(fā)送到FPGA,以便FPGA可以執(zhí)行諸如濾波或顏色平面提取等操作。然后,您可以將圖像發(fā)送回CPU以進(jìn)行更高級(jí)的操作,例如光學(xué)字符識(shí)別(OCR)或模式匹配。

在某些情況下,您可以在FPGA上實(shí)現(xiàn)所有的處理步驟,并只將處理結(jié)果發(fā)送回CPU。這使得CPU可以將更多的資源用于運(yùn)動(dòng)控制、網(wǎng)絡(luò)通信和圖像顯示等其他操作。

圖1.在FPGA協(xié)處理中,圖像使用CPU進(jìn)行采集后,通過DMA發(fā)送到FPGA,然后由FPGA對(duì)圖像進(jìn)行處理。

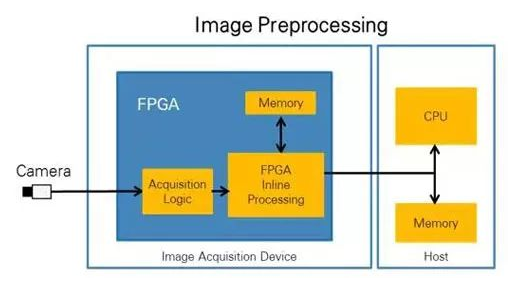

在嵌入式FPGA處理架構(gòu)中,您可以將相機(jī)接口直接連接到FPGA的引腳,以便像素可直接從相機(jī)發(fā)送到FPGA。這種架構(gòu)通常與Camera Link相機(jī)一起使用,因?yàn)樗鼈兊牟杉壿嬕子谑褂肍PGA上的數(shù)字電路來實(shí)現(xiàn)。 這個(gè)架構(gòu)有兩個(gè)主要的好處:

首先,與協(xié)處理一樣,在FPGA上執(zhí)行預(yù)處理功能時(shí),可以使用嵌入式處理將部分工作從CPU轉(zhuǎn)移到FPGA。例如,在將像素發(fā)送到CPU之前,可以在FPGA上執(zhí)行高速預(yù)處理,如濾波或閾值處理。這也減少了CPU必須處理的數(shù)據(jù)量,因?yàn)镃PU上的邏輯只需捕獲感興趣區(qū)域的像素,這最終提高了整個(gè)系統(tǒng)的吞吐量。

這種架構(gòu)的第二個(gè)好處是可以在不使用CPU的情況下直接在FPGA內(nèi)進(jìn)行高速控制操作。FPGA是控制應(yīng)用的理想選擇,因?yàn)樗鼈兛梢蕴峁┓浅?焖偾腋叨却_定的循環(huán)速率。其中一個(gè)例子就是高速分類,其中FPGA向執(zhí)行器發(fā)送脈沖,當(dāng)脈沖通過執(zhí)行器時(shí),執(zhí)行器會(huì)對(duì)零件進(jìn)行剔除或分類操作。

圖2.在嵌入式FPGA處理架構(gòu)中,您可以將相機(jī)接口直接連接到FPGA的引腳,以便像素可直接從相機(jī)發(fā)送到FPGA。

2、CPU與FPGA視覺算法

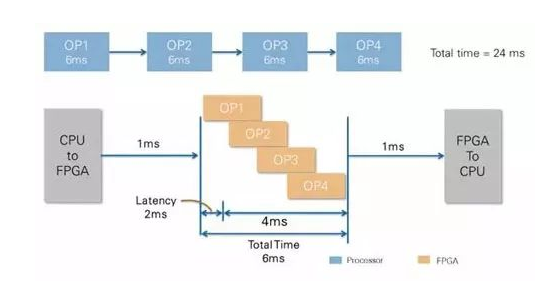

在對(duì)構(gòu)建異構(gòu)視覺系統(tǒng)的不同方式有了基本了解,您可以看一下在FPGA上運(yùn)行的最佳算法。 首先需要了解CPU和FPGA的工作原理。 為了解釋這一概念,我們假設(shè)一個(gè)理論算法可對(duì)圖像執(zhí)行四個(gè)不同的操作,然后看一下這四個(gè)操作部署到CPU和FPGA上時(shí)分別是如何運(yùn)行的:

CPU按順序執(zhí)行操作,因此第一個(gè)操作必須在整個(gè)圖像上運(yùn)行結(jié)束后,第二個(gè)操作才能啟動(dòng)。在本例中,假設(shè)算法中的每個(gè)步驟在CPU上運(yùn)行需要6ms; 因此,總處理時(shí)間是24ms。

現(xiàn)在考慮在FPGA上運(yùn)行相同的算法。由于FPGA本質(zhì)上是大規(guī)模并行的,所以該算法中的四個(gè)操作可以同時(shí)對(duì)圖像中的不同像素上操作。這意味著接收第一個(gè)處理的像素僅需2ms的時(shí)間,處理整個(gè)圖像需要4ms的時(shí)間,因而總處理時(shí)間為6ms。這比CPU的執(zhí)行速度快得多。

即使使用FPGA協(xié)處理架構(gòu)并將圖像傳輸?shù)紺PU,整個(gè)處理時(shí)間(包括傳輸時(shí)間)也比單獨(dú)使用CPU要短得多。

圖3.由于FPGA在本質(zhì)上是大規(guī)模并行的,因此相比CPU,可顯著性能提升。

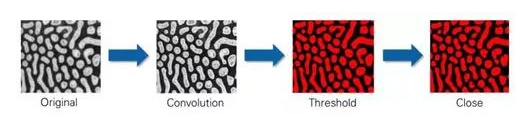

現(xiàn)在考慮一個(gè)真實(shí)的例子,比如粒子計(jì)數(shù)所需的圖像。首先需要應(yīng)用卷積濾鏡來銳化圖像。接下來,通過閾值運(yùn)行圖像以生成二進(jìn)制圖像。這不僅可以通過將其從8位單色轉(zhuǎn)換為二進(jìn)制來減少圖像中的數(shù)據(jù)量,還可以為二進(jìn)制形態(tài)學(xué)應(yīng)用準(zhǔn)備圖像。最后一步是使用形態(tài)學(xué)來應(yīng)用關(guān)閉功能。 這會(huì)去除二進(jìn)制粒子中的任何孔。

如果僅在CPU上執(zhí)行上述算法,則必須在閾值步驟開始之前完成整個(gè)圖像的卷積步驟。使用NI公司面向LabVIEW的視覺開發(fā)模塊(Vision Development Module)和基于Xilinx Zynq-7020全可編程SoC的cRIO-9068 CompactRIO控制器時(shí),執(zhí)行上述算法需要的時(shí)間為166.7ms。

但是,如果在FPGA上運(yùn)行相同的算法,則可以并行執(zhí)行每個(gè)步驟。在FPGA上運(yùn)行相同的算法只需8ms即可完成。請(qǐng)記住,8ms的時(shí)間中包括將圖像從CPU發(fā)送到FPGA的DMA傳輸時(shí)間,以及算法完成的時(shí)間。在某些應(yīng)用中,可能需要將處理后的圖像發(fā)回到CPU,以供應(yīng)用中的其他部分使用。如果加上這個(gè)時(shí)間的話,整個(gè)過程也只需8.5ms。總的來說,F(xiàn)PGA執(zhí)行這個(gè)算法要比CPU快20倍。

圖4:使用FPGA協(xié)同處理架構(gòu)運(yùn)行視覺算法,性能比僅用CPU運(yùn)行同樣的算法提高了20倍。

3、那么,為什么不在FPGA上運(yùn)行每個(gè)算法呢?

盡管FPGA比CPU更有益于視覺處理,但是要享受這些優(yōu)勢(shì)也要做出一定的權(quán)衡。例如,考慮CPU與FPGA的原始時(shí)鐘頻率。FPGA的時(shí)鐘頻率在100~200MHz數(shù)量級(jí)。很顯然,F(xiàn)PGA的時(shí)鐘頻率低于CPU的時(shí)鐘頻率,CPU可以輕松地在3GHz或更高的頻率下運(yùn)行。因此,如果一個(gè)應(yīng)用需要一種必須迭代運(yùn)行的圖像處理算法,并且不能利用FPGA的并行性,那么CPU能夠更快地進(jìn)行處理。

前面討論的示例算法在FPGA上運(yùn)行可以獲得20倍的速度提升。該算法中的每個(gè)處理步驟同時(shí)對(duì)各個(gè)像素或一組像素進(jìn)行操作,因此該算法可以利用FPGA的并行優(yōu)勢(shì)來處理圖像。 然而,如果算法使用諸如模式匹配和OCR這樣的處理步驟,這些要求立即分析整個(gè)圖像,這時(shí)候FPGA的優(yōu)勢(shì)就比較勉強(qiáng)了。這是由于缺少處理步驟的并行化,以及需要大量?jī)?nèi)存進(jìn)行圖像與模板之間的比對(duì)分析。

雖然FPGA可以直接訪問內(nèi)部和外部存儲(chǔ)器,但通常情況下,F(xiàn)PGA可用的存儲(chǔ)器數(shù)量遠(yuǎn)不及CPU可用的數(shù)量,或是這些處理操作所需的數(shù)量。

4、克服編程復(fù)雜性

FPGA用于圖像處理的優(yōu)勢(shì),取決于每種應(yīng)用要求,包括應(yīng)用的特定算法、延遲或抖動(dòng)要求、I/O同步和功耗等因素。通常使用具有FPGA和CPU的架構(gòu),能充分利用FPGA和CPU各自的優(yōu)勢(shì),并且在性能、成本和可靠性方面都具有競(jìng)爭(zhēng)優(yōu)勢(shì)。然而,實(shí)現(xiàn)基于FPGA的視覺系統(tǒng)面臨的最大挑戰(zhàn)之一是克服FPGA的編程復(fù)雜性。

視覺算法開發(fā)本質(zhì)上是一個(gè)迭代過程。完成任何一項(xiàng)任務(wù)都必須嘗試多種方法。大多數(shù)情況下,需要確定的不是哪種方法可行,而是哪種方法最好,而“最好方法”的判定則因應(yīng)用的不同而不同。例如,對(duì)于某些應(yīng)用而言,速度至關(guān)重要;而對(duì)于另一些應(yīng)用,則更看重準(zhǔn)確度。至少,需要嘗試幾種不同的方法才能為特定應(yīng)用找到最好的方法。

因此在考慮誰更適合進(jìn)行圖像處理時(shí),CPU還是FPGA?答案是“視情況而定”。您需要了解應(yīng)用的目標(biāo),才能使用最適合該設(shè)計(jì)的處理元件。但是,不管是什么應(yīng)用,基于CPU或FPGA的架構(gòu)及其固有的優(yōu)勢(shì)都可以將機(jī)器視覺應(yīng)用的性能提升一個(gè)等級(jí)。